HAL driver APIs ¶

Initialization and deinitialization APIs ¶

HAL PPP initialization ¶

The HAL_PPP_Init function is the first API called to initialize a given instance of the HAL PPP driver. The scope of the HAL_PPP_Init API is limited to associating a given peripheral instance with the handle object and initializing this software object. The HAL_PPP_Init function does not configure the peripheral; this is the purpose of the configuration API. However, HAL_PPP_Init can activate the peripheral clock upon user demand using a dedicated compilation switch.

The HAL_PPP_Init APIs perform the following actions:

Check handle and PPP instance validity using asserts.

Associate the HAL PPP instance with the HAL PPP handle.

If the compilation switch USE_HAL_PPP_CLK_ENABLE_MODEL is set to a value equal to or greater than HAL_CLK_ENABLE_PERIPH_ONLY, enable the PPPi clock using the dedicated LL or HAL PPPi clock enabling APIs.

If the given peripherals have dependencies on the system and PWR, and the compilation switch is set to HAL_CLK_ENABLE_PERIPH_PWR_SYSTEM , then the additional PWR and system components needed to make the peripheral work should be enabled.

Set default callbacks to the weak default callbacks. Callbacks can be updated after initialization if needed using HAL_PPP_RegisterEventiCallback APIs when this feature is enabled.

Initialize the handle fields (states or any other internal fields used during various possible HAL processes).

Including initializing the “User Data pointer” (p_user_data) to NULL.

Resetting the last_error_codes variable storing the last errors.

Set the sub-instances or processes states if any to RESET, and finally, set the global HAL PPP state within the handle to HAL_PPP_STATE_INIT, indicating that the HAL PPP driver is initialized for the current handle object but not yet ready to start a process, as it requires configuration.

/**

* @brief Initialize the PPP handle and associate an instance.

* @param hppp pointer to a hal_ppp_handle_t structure.

* @param instance one of the values of the enumeration hal_ppp_t .

* @retval HAL_OK HAL PPP initialization done

* @retval HAL_INVALID_PARAM when the hppp handle is NULL

*/

hal_status_t HAL_PPP_Init(hal_ppp_handle_t *hppp, hal_ppp_t instance)

{

/* Check the PPP handle allocation */

ASSERT_DBG_PARAM((hppp != NULL));

/* Check the PPP instance */

ASSERT_DBG_PARAM(IS_PPP_INSTANCE((PPP_TypeDef *) ((uint32_t)instance)));

#if defined(USE_HAL_CHECK_PARAM) && (USE_HAL_CHECK_PARAM ==1)

/* Check the handle struct pointer */

if(hppp == NULL)

{

return HAL_INVALID_PARAM;

}

#endif /* USE_HAL_CHECK_PARAM */

hppp->instance = instance;

#if defined (USE_HAL_PPP_REGISTER_CALLBACKS) && (USE_HAL_PPP_REGISTER_CALLBACKS == 1)

/* Init the PPP Callback settings */

hppp->p_event_i_cb = HAL_PPP_EventiCallback; /* Event_i callback reset */

(...)

hppp->p_error_cb = HAL_PPP_ErrorCallback; /* Error callback reset */

#endif /* USE_HAL_PPP_REGISTER_CALLBACKS */

/* Init the handle internal parameters */

hppp->param_i = VALUE;

(...)

#if defined (USE_HAL_PPP_USER_DATA) && (USE_HAL_PPP_USER_DATA == 1)

/* Init the user data pointer to NULL */

hppp->p_user_data = NULL;

#endif

(...)

#if defined (USE_HAL_PPP_GET_LAST_ERRORS) && (USE_HAL_PPP_GET_LAST_ERRORS == 1)

/* Reset the last_error_codes variable storing the last errors */

hspi->last_error_codes = HAL_PPP_ERROR_NONE;

#endif /* USE_HAL_PPP_GET_LAST_ERRORS */

#if defined(USE_HAL_SPIPPP_CLK_ENABLE_MODEL) && (USE_HAL_SPIPPP_CLK_ENABLE_MODEL >= HAL_CLK_ENABLE_PERIPH_ONLY)

/* Enable the PPP Peripheral Clock */

switch (hppp->instance)

{

#if defined(PPP1)

case HAL_SPI1:

/* Enable Clock */

LL_APB2_GRP1_EnableClock(LL_APB2_GRP1_PERIPH_PPP1);

break;

#endif /* PPP1 */

(...)

}

#endif

#if defined (USE_HAL_PPP_DMA) && (USE_HAL_PPP_DMA == 1)

hppp->hdma_i = NULL; /*!< Init the process i DMA handle to NULL */

#endif /* USE_HAL_PPP_DMA */

/* Init the subinstances states when available */

hppp->subinstance_states[0] = HAL_PPP_SUBINSTANCE_STATE_RESET;

(...)

hppp->subinstance_states[nb_subinstance] = HAL_PPP_SUBINSTANCE_STATE_RESET;

/* Or Init the subinstance single state variable when available */

hppp->subinstance_state = HAL_PPP_SUBINSTANCE_STATE_RESET;

/* Or Init the processes states when available */

hppp->process_i_state = HAL_PPP_STATE_PROCESSi_RESET;

(...)

hppp->process_j_state = HAL_PPP_STATE_PROCESSi_RESET;

/* Init the global state */

hppp->global_state = HAL_PPP_STATE_INIT;

return HAL_OK;

}

HAL PPP deinitialization ¶

The HAL_PPP_DeInit service should be used to de-initialize a given instance of the HAL PPP driver when a HAL_PPP_Init service exists. The HAL_PPP_DeInit service performs the following actions:

Check handle and PPP instance validity using asserts.

Stop Current Operations:

Invoke the required private routines to stop or abort any ongoing process. This includes disabling the IP, disabling interrupts, and clearing flags.

Alternatively, implement the stop/abort directly within HAL_PPP_DeInit using a sequence of LL calls or by writing to the required registers/fields.

Note: Do not call public APIs HAL_PPP_Stop or HAL_PPP_Abort to avoid state machine conflicts as each public API has its own state checks.

Note: the stop and abort of ongoing processes should take into consideration stopping/aborting the DMA if used by the given driver and ongoing process (meaning that corresponding DMA handle used by the PPP handle goes back to IDLE state once the parent HAL_PPP is de-initialized).

Delete Bus Semaphore: If USE_HAL_MUTEX is set to 1, delete the bus semaphore for the bus drivers’ category.

Reset Handle State: Reset the handle’s global state, process state, and sub-instance(s) states (if any).

Set the global HAL PPP state and sub-instance(s) within the handle to HAL_PPP_STATE_RESET, indicating that the HAL PPP driver is de-initialized for the current handle object.

A new initialization and configuration sequence is required to reuse this handle object.

Therefore, it is not necessary to clean other internal fields within the HAL PPP handle during HAL_PPP_DeInit , as this clean-up is already performed in HAL_PPP_Init (including the internal counters and pointers, internal variables and callback pointers).

Note

The HAL_PPP_DeInit function forces stopping any ongoing operation and restores the state machine to their default/reset states. Therefore, this function does not ASSERT on any state.

The resources de-initialization (DMA, GPIO, NVIC, CLOCK) and the peripheral reset (using RCC force/release reset) are handled by the user application, typically implemented in the mx_pppi_deinit() function generated by STM32CubeMX.

void HAL_PPP_DeInit(hal_ppp_handle_t *hppp)

{

/* Check the PPP handle allocation */

ASSERT_DBG_PARAM((hppp != NULL));

/* Check the PPP instance */

ASSERT_DBG_PARAM(IS_PPP_INSTANCE((PPP_TypeDef *) ((uint32_t)hppp->instance)));

/* Stop current process/operation(s) */

(void) PPP_Disable(hppp);

/* or */

(void) PPP_Stop(hppp);

/* or */

(void) PPP_Abort(hppp);

/* or*/

/* Write needed registers/fields to stop any ongoing process */

#if defined(USE_HAL_MUTEX) && (USE_HAL_MUTEX == 1)

/* Delete the PPP semaphore */

(void)HAL_OS_SemaphoreDelete(&hppp->semaphore);

#endif /* USE_PPP_MUTEX */

/* Reset the subinstances states when available */

hppp->subinstance_states[0] = HAL_PPP_SUBINSTANCE_STATE_RESET;

(...)

hppp->subinstance_states[nb_subinstance] = HAL_PPP_SUBINSTANCE_STATE_RESET;

/* Or Reset the subinstance state unique when available */

hppp->subinstance_state = HAL_PPP_SUBINSTANCE_STATE_RESET;

/* Or Reset the processes states when available */

hppp->process_i_state = HAL_PPP_STATE_PROCESSi_RESET;

(...)

hppp->process_j_state = HAL_PPP_STATE_PROCESSj_RESET;

/* Reset the global state */

hppp->global_state = HAL_PPP_STATE_RESET;

}

HAL PPP instance retrieval ¶

In some HAL drivers based on a handle, there could be some APIs that use the HAL instance directly. These APIs are for security attribute settings or, in the case of HAL FLASH, to provide control APIs such as unlock APIs or option-byte programming APIs. To retrieve the HAL instance from the handle, the following function is provided:

hal_ppp_t HAL_PPP_GetInstance(const hal_ppp_handle_t *hppp)

{

ASSERT_DBG_PARAM((hppp != NULL));

ASSERT_DBG_PARAM(IS_PPP_ALL_INSTANCE((PPP_TypeDef *)((uint32_t)hppp->instance)));

return hppp->instance;

}

Additionally, for users that need to cohabitate HAL and LL drivers, the following functions are provided to retrieve the CMSIS/LL PPP_TypeDef instance:

Case of a handle-based driver (Ex: I2C, UART …): retrieve the CMSIS/LL PPP_TypeDef instance from the HAL PPP handle (hal_ppp_handle_t)

PPP_TypeDef *HAL_PPP_GetLLInstance(const hal_ppp_handle_t *hppp)

{

ASSERT_DBG_PARAM((hppp != NULL));

ASSERT_DBG_PARAM(IS_PPP_ALL_INSTANCE((PPP_TypeDef *)((uint32_t)hppp->instance)));

return ((PPP_TypeDef *)((uint32_t)((hppp)->instance)));

}

Case of a driver not based on a handle (Ex HAL RAMCFG): retrieve the CMSIS/LL PPP_TypeDef instance from the HAL PPP instance (hal_ppp_t)

PPP_TypeDef *HAL_PPP_GetLLInstance(hal_ppp_t instance)

{

ASSERT_DBG_PARAM(IS_PPP_ALL_INSTANCE((PPP_TypeDef *)((uint32_t)instance)));

return ((PPP_TypeDef *)((uint32_t)(instance)));

}

Configuration APIs ¶

HAL PPP global configuration ¶

The global configuration APIs, HAL_PPP_SetConfig and HAL_PPP_GetConfig , are provided to apply or retrieve a configuration that is applicable for the entire peripheral instance.

HAL_PPP_SetConfig Actions:

Parameter Check: use dedicated ASSERT_DBG_PARAM to check API parameters, which can be enabled in debug mode using a dedicated compilation switch to reduce footprint in the final release application.

State Check: ensure the global state is HAL_PPP_STATE_INIT or HAL_PPP_STATE_IDLE using ASSERT_DBG_STATE, which can be enabled in debug mode using a dedicated compilation switch to reduce footprint in the final release application.

Sub-instance State Check: when several sub-instances are available, use ASSERT_DBG_STATE to check that the sub-instances are not in the ACTIVE state (no sub-instance(s) running).

Process State Check: when several process states are available, use ASSERT_DBG_STATE to check that the processes are in the IDLE state (no process running).

Config Structure Pointer Parameter check: verify that the config structure pointer is not NULL (as it is a vital parameter and may lead to a hard fault if null) and return HAL_INVALID_PARAM status in case of NULL.

This check shall be done under the compilation switch USE_HAL_CHECK_PARAM to reduce footprint when the user wants to bypass this check. Other parameters are checked by assert , including the handle that was already checked during HAL_PPP_Init .

Peripheral Disable: disable the peripheral if mandatory to update the configuration registers.

Update Configuration registers: update the required peripheral configuration/control registers according to the user configuration structure (using the appropriate LL configuration APIs).

Handle Update: depending on the HAL_PPP handle and implementation, update the handle internal variable used by the process according to the user configuration if needed.

Peripheral Enable: enable the peripheral once the configuration is applied if required by the peripheral.

Confirmation Flag Check: depending on the peripheral, the configuration may require waiting for a confirmation flag(s) (delayed configuration).

In this case, a wait loop should be used to confirm the configuration through the dedicated peripheral flag(s). Use an intrinsic timeout define ( HAL_PPP_FLAG_TIMEOUT ), implemented in stm32tnxx_hal_ppp.c with respect to the peripheral/product spec (not a public define).

When the dedicated flag(s) are confirmed, set the global state to HAL_PPP_STATE_IDLE and return HAL_OK . If an error occurs during the global configuration (a confirmation flag doesn’t rise), return HAL_ERROR .

Immediate Configuration: when all the configuration registers take effect immediately (no need to wait for a confirmation flag), set the global state to HAL_PPP_STATE_IDLE at the end of the configuration and return HAL_OK.

Note

Context HAL2 versus HAL1: there are no more MspInit callbacks in HAL2 drivers. The equivalent Clock/GPIO/NVIC/DMA settings are inserted before HAL_PPP_Init or between HAL_PPP_Init and HAL_PPP_SetConfig .

hal_status_t HAL_PPP_SetConfig(hal_ppp_handle_t *hppp, const hal_ppp_config_t *p_config)

{

uint32_t tick_start; /* Only when need to wait on flag for a delayed configuration */

PPP_TypeDef *p_pppx;

/* Check the PPP handle and config allocation */

ASSERT_DBG_PARAM((hppp != NULL));

ASSERT_DBG_PARAM((p_config != NULL));

/* Check the parameters */

ASSERT_DBG_PARAM(IS_PPP_PARAMi(p_config->param_i));

/* Check the global state */

ASSERT_DBG_STATE(hppp->global_state, (uint32_t)HAL_PPP_STATE_INIT | (uint32_t)HAL_PPP_STATE_IDLE);

/* Check the Sub-Instance state when available */

/* case of multi subinstances variables */

ASSERT_DBG_STATE(hppp->subinstance_states[0], (uint32_t)HAL_PPP_SUBINSTANCE_STATE_RESET |

(uint32_t)HAL_PPP_SUBBLOCKi_SUBINSTANCE_STATE_IDLE |

(uint32_t)HAL_PPP_SUBBLOCKj_SUBINSTANCE_STATE_IDLE);

(...)

ASSERT_DBG_STATE(hppp->subinstance_states[nb_subinstance], (uint32_t)HAL_PPP_SUBINSTANCE_STATE_RESET |

(uint32_t)HAL_PPP_SUBBLOCKi_SUBINSTANCE_STATE_IDLE |

(uint32_t)HAL_PPP_SUBBLOCKj_SUBINSTANCE_STATE_IDLE);

/* Or case of a single subinstance variable */

ASSERT_DBG_STATE(hppp->subinstance_state, (uint32_t)HAL_PPP_SUBINSTANCE_STATE_RESET |

(uint32_t)HAL_PPP_SUBBLOCKi_SUBINSTANCE_STATE_IDLE |

(uint32_t)HAL_PPP_SUBBLOCKj_SUBINSTANCE_STATE_IDLE);

/* Or Check the Processes states when available */

ASSERT_DBG_STATE(hppp->process_i_state, HAL_PPP_STATE_PROCESS_IDLE);

#if defined(USE_HAL_CHECK_PARAM) && (USE_HAL_CHECK_PARAM == 1)

/* check the config struct pointer */

if(p_config == NULL)

{

return HAL_INVALID_PARAM;

}

#endif /* USE_HAL_CHECK_PARAM */

p_pppx = PPP_GET_INSTANCE(hppp);

/* Disable The PPP instance if mandatory by the peripheral to Update the configuration registers */

LL_PPP_Disable((p_pppx));

/* Call the LL to set the configuration items with adjustment if required */

LL_PPP_ConfigItem(p_pppx, ADJ(conf->param_i, p_config->param_j));

(...)

LL_PPP_SetItem(p_pppx, ADJ(p_config->param_k));

(...)

/* Enable the peripheral once the configuration applied if required by the peripheral */

LL_PPP_Enable(p_pppx);

/* if needed: Update the handle internal parameters according to the user config (with adjustment if required) */

hppp->param_i = ADJ(p_config->param_i);

(...)

//////////////// Case 1 //////////////////

/* When needed wait for a delayed configuration to be completed

(by checking PPP flag field)

*/

tick_start = HAL_GetTick();

do

{

if(LL_PPP_IsActiveFlag_BITNAME(p_pppx) == SET)

{

/* Update The HAL PPP global State */

hppp->global_state = HAL_PPP_STATE_IDLE;

return HAL_OK;

}

} while ((HAL_GetTick() - tick_start) <= HAL_PPP_FLAG_TIMEMOUT);

return HAL_ERROR;

//////////////// End of Case 1 ///////////

//////////////// Case 2 //////////////////

/* The configuration is immediate: no flags to be checked */

/* Update The HAL PPP global State */

hppp->global_state = HAL_PPP_STATE_IDLE;

return HAL_OK;

//////////////// End of Case 2 ///////////

}

Note

Immediate Use: Depending on the peripheral, it can be used immediately after the global configuration (e.g., UART).

Sub-block Configuration: Some peripherals (e.g., TIM) require a global configuration and may also require at least one channel configuration if used in output or input compare mode.

The HAL_PPP_GetConfig API retrieves the global configuration and performs the following actions:

Check the API parameters using dedicated assertions that can be enabled in debug mode, reducing the footprint in the final “release” application.

Ensure that the global state is HAL_PPP_STATE_IDLE or HAL_PPP_STATE_ACTIVE, meaning that a valid global configuration has been applied.

Read the required peripheral configuration/control registers using the corresponding LL APIs and update the user configuration structure.

Note

Depending on the HAL PPP handle and implementation, the handle’s internal variables may also be needed to update (reconstruct) the user configuration structure in addition to the values read from the peripheral registers.

Note

Depending on the HAL PPP handle design and implementation, some internal handle variables may also be needed to fully reconstruct the user configuration structure in addition to values read back from the peripheral registers.

void HAL_PPP_GetConfig(hal_ppp_handle_t *hppp, hal_ppp_config_t *p_config)

{

uint32_t config;

PPP_TypeDef *p_pppx;

/* Check the PPP handle & config allocation */

ASSERT_DBG_PARAM((hppp != NULL));

ASSERT_DBG_PARAM((p_config != NULL));

/* Check the global state */

ASSERT_DBG_STATE(hppp->global_state, (uint32_t)HAL_PPP_STATE_IDLE |

(uint32_t)HAL_PPP_STATE_ACTIVE);

/* Call the LL to Get the configuration items with

adjustment if required */

p_pppx = PPP_GET_INSTANCE(hppp);

config = LL_PPP_GetConfigItem(p_pppx, ...);

p_config->param_i = ADJ_i(config);

p_config->param_j = ADJ_j(config);

(...)

p_config->param_k = ADJ_k(p_pppx);

}

HAL PPP configuration reset ¶

void HAL_PPP_ResetConfig(hal_ppp_handle_t *hppp)

{

PPP_TypeDef *p_pppx;

/* Check the PPP handle allocation */

ASSERT_DBG_PARAM(hppp != NULL);

/* Check the global state */

ASSERT_DBG_STATE(hppp->global_state, HAL_PPP_STATE_IDLE);

/* Check the Sub-Instance state when available */

/* case of multi subinstances variables */

ASSERT_DBG_STATE(hppp->subinstance_states[0], (uint32_t)HAL_PPP_SUBINSTANCE_STATE_RESET |

(uint32_t)HAL_PPP_SUBBLOCKi_SUBINSTANCE_STATE_IDLE |

(uint32_t)HAL_PPP_SUBBLOCKj_SUBINSTANCE}_STATE_IDLE);

(...)

ASSERT_DBG_STATE(hppp->subinstance_states[nb_subinstance], (uint32_t)HAL_PPP_SUBINSTANCE_STATE_RESET |

(uint32_t)HAL_PPP_SUBBLOCKi_SUBINSTANCE_STATE_IDLE |

(uint32_t)HAL_PPP_SUBBLOCKj_SUBINSTANCE_STATE_IDLE);

/* Or case of a single subinstance variable */

ASSERT_DBG_STATE(hppp->subinstance_state, (uint32_t)HAL_PPP_SUBINSTANCE_STATE_RESET |

(uint32_t)HAL_PPP_SUBBLOCKi_SUBINSTANCE_STATE_IDLE |

(uint32_t)HAL_PPP_SUBBLOCKj_SUBINSTANCE_STATE_IDLE);

/* Or Check the Processes states when available */

ASSERT_DBG_STATE(hppp->process_i_state, HAL_PPP_STATE_PROCESS_IDLE);

p_pppx = PPP_GET_INSTANCE(hppp);

/* Reset the configuration items to their default/HW reset values */

/* either using config or unitary LL APIS */

LL_PPP_ConfigItem(p_pppx, param_i_reset_val, param_j_reset_val);

(...)

LL_PPP_SetItem(p_pppx, param_k_reset_val);

/* or using LL_WriteReg APIs when the config parameters are located in the same register */

LL_PPP_WriteReg(p_pppx, REG_X, REG_X_RESET_VAL);

}

HAL PPP sub-block configuration ¶

The sub-block configuration APIs are used to configure a PPP sub-block. Depending on the peripheral, a sub-block can be composed of or linked to several sub-instances. In such cases, the “sub-instance” should be included in the sub-block configuration API naming and parameters (e.g., a TIMER output compare channel or an ADC channel). Two APIs, HAL_PPP_{SUBBLOCK}_SetConfig{Subinstance} and HAL_PPP_{SUBBLOCK}_GetConfig{Subinstance} , are provided per sub-block to apply and retrieve the sub-block configuration, respectively.

The HAL_PPP_{SUBBLOCK}_SetConfig{Subinstance} API performs the following actions:

As with the global config API, check the API parameters using dedicated assertions that can be enabled in debug mode, reducing the footprint in the final “release” application.

Ensure that the global state is HAL_PPP_STATE_IDLE (using dedicated assertions), meaning that a global configuration has already been applied to proceed with the sub-block and sub-instance configuration.

Verify that the sub-instance is not in the “ACTIVE” state (using dedicated assertions).

As with the global config API, check the config structure pointer against NULL and return HAL_INVALID_PARAM status in case of NULL (other parameters are checked only by assertions, including the handle that was already checked during the HAL_PPP_Init).

Update the required peripheral configuration/control registers according to the user configuration structure (using the appropriate LL configuration APIs).

Depending on the HAL PPP handle and implementation, update the handle’s internal variables used by the process according to the user configuration, if needed.

Depending on the peripheral, the configuration may require waiting for a confirmation flag(s) (delayed configuration). In this case, a wait loop is used to confirm the configuration through the dedicated peripheral flag(s).

An intrinsic timeout define ( HAL_PPP_FLAG_TIMEOUT ) is used, implemented in the stm32tnxx_hal_ppp.c file with respect to the peripheral/product specification (not a public define). When the dedicated flag(s) are confirmed, the sub-instance state changes to “IDLE” and the API returns HAL_OK . If an error occurs (a confirmation flag doesn’t rise), the API returns HAL_ERROR .

When all the configuration registers of the given peripheral take effect immediately (no need to wait for a confirmation flag), the sub-state changes to “IDLE” at the end of the configuration, and the API returns HAL_OK.

hal_status_t HAL_PPP_{SUBBLOCK}_SetConfig{Subinstance}(hal_ppp_handle_t *hppp,

hal_ppp_{subinstance}_t subinstance,

const hal_ppp_{subblock}_{subinstance}_config_t *p_config)

{

uint32_t tick_start; /* Only when need to wait on flag for a delayed configuration */

PPP_TypeDef *p_pppx;

/* Check the PPP handle & config allocation */

ASSERT_DBG_PARAM((hppp != NULL));

ASSERT_DBG_PARAM((p_config != NULL));

/* Check the Subinstance parameter */

ASSERT_DBG_PARAM(IS_PPP_SUBBLOCK_SUBINSTANCE(subinstance));

/* Check configuration parameters */

ASSERT_DBG_PARAM(IS_PPP_SUBBLOCK_PARAMi(p_config->param_i));

/* Check the global state: should be IDLE (already globally configured) */

ASSERT_DBG_STATE(hppp->global_state, HAL_PPP_STATE_IDLE);

/* Check the Sub-Instance state */

/* Case of multi subinstances variable */

ASSERT_DBG_STATE(hppp->subinstance_states[subinstance], (uint32_t)HAL_PPP_SUBINSTANCE_STATE_RESET |

(uint32_t)HAL_PPP_SUBBLOCKi_SUBINSTANCE_STATE_IDLE |

(uint32_t)HAL_PPP_SUBBLOCKj_SUBINSTANCE_STATE_IDLE);

/* Or case of a single subinstance variable */

ASSERT_DBG_STATE(hppp->subinstance_state, (uint32_t)HAL_PPP_SUBINSTANCE_STATE_RESET |

(uint32_t)HAL_PPP_SUBBLOCKi_SUBINSTANCE_STATE_IDLE |

(uint32_t)HAL_PPP_SUBBLOCKj_SUBINSTANCE_STATE_IDLE);

#if defined(USE_HAL_CHECK_PARAM) && (USE_HAL_CHECK_PARAM == 1)

/* Check the config struct pointer (runtime) */

if (p_config == NULL)

{

return HAL_INVALID_PARAM;

}

#endif /* USE_HAL_CHECK_PARAM */

p_pppx = PPP_GET_INSTANCE(hppp);

/* Optionally disable the sub-block or related functional unit if mandatory before reconfiguration */

/* LL_PPP_SUBBLOCK_Disable(p_pppx, subinstance); */

/* Call the LL to set the SUBBLOCK/Subinstance configuration items with adjustment if required */

LL_PPP_SUBBLOCK_ConfigItem(p_pppx, subinstance, ADJ(p_config->param_i, p_config->param_j));

(...)

LL_PPP_SUBBLOCK_SetItem(p_pppx, subinstance, ADJ(p_config->param_k));

(...)

/* If needed: update handle internal parameters according to the user config (with adjustment if required) */

hppp->param_i = ADJ(p_config->param_i);

(...)

//////////////// Case 1 //////////////////

/* Delayed configuration path: wait for a confirmation flag */

tick_start = HAL_GetTick();

do

{

if (LL_PPP_IsActiveFlag_BITNAME(p_pppx) == SET)

{

/* Update the subinstance state */

/* Case of multi subinstances variable */

hppp->subinstance_states[subinstance] = HAL_PPP_SUBBLOCKi_SUBINSTANCE_STATE_IDLE;

/* Or case of a single subinstance variable */

hppp->subinstance_state = HAL_PPP_SUBBLOCKi_SUBINSTANCE_STATE_IDLE;

return HAL_OK;

}

} while ((HAL_GetTick() - tick_start) <= HAL_PPP_FLAG_TIMEOUT);

/* In case of timeout / error */

return HAL_ERROR;

//////////////// End of Case 1 ///////////

//////////////// Case 2 //////////////////

/* Immediate configuration path: no flag to be checked */

/* Update the subinstance state */

/* Case of multi subinstances variable */

hppp->subinstance_states[subinstance] = HAL_PPP_SUBBLOCKi_SUBINSTANCE_STATE_IDLE;

/* Or case of a single subinstance variable */

hppp->subinstance_state = HAL_PPP_SUBBLOCKi_SUBINSTANCE_STATE_IDLE;

return HAL_OK;

//////////////// End of Case 2 ///////////

}

The HAL_PPP_{SUBBLOCK}_GetConfig{Subinstance} API performs the following actions:

Check the API parameters using dedicated assertions that can be enabled in debug mode, reducing the footprint in the final “release” application.

Ensure that the global state is “IDLE” or above, meaning that a valid global configuration has been applied (using dedicated assertions).

Verify that the sub-instance state is not “RESET”, indicating that a valid sub-instance configuration has been applied (using assertions).

Read the required peripheral configuration/control registers using the corresponding LL APIs and update the user configuration structure.

Note

Depending on the HAL PPP handle design and implementation, some internal handle variables may be required (in addition to values read from peripheral registers) to fully reconstruct the user configuration structure.

void HAL_PPP_{SUBBLOCK}_GetConfig{Subinstance}(hal_ppp_handle_t *hppp,

hal_ppp_{subinstance}_t Subinstance,

hal_ppp_{subblock}_{subinstance}_config_t *p_config)

{

uint32_t config;

PPP_TypeDef *p_pppx;

/* Check the PPP handle & config allocation */

ASSERT_DBG_PARAM((hppp != NULL));

ASSERT_DBG_PARAM((p_config != NULL));

/* Check the Subinstance */

ASSERT_DBG_PARAM(IS_PPP_SUBBLOCK_SUBINSTANCE(Subinstance));

/* Check the global state */

/* Check the Sub-Instance state */

/* case of multi subinstances variables */

/* Call the LL to Get the configuration items with adjustment if required */

p_pppx = PPP_GET_INSTANCE(hppp);

config = LL_PPP_SUBBLOCK_GetConfigItem((PPP_TypeDef *)((uint32_t)hppp->instance), ...);

p_config->param_i = ADJ_i(config);

p_config->param_j = ADJ_j(config);

(...)

p_config->param_k = ADJ_k(LL_PPP_SUBBLOCK_GetItem((PPP_TypeDef *)((uint32_t)hppp->instance)));

}

HAL PPP unitary configuration ¶

The unitary configuration APIs allow configuring or retrieving a single item for a given peripheral, such as setting the UART baud rate. Depending on the peripheral, the unitary item can be applicable to the entire PPP instance, a specific sub-block, or a sub-instance of a sub-block. These APIs are intended to dynamically modify or retrieve a unitary item, meaning that a global or sub-block configuration has already been applied. Unitary configuration APIs first check if the corresponding state is “IDLE” (indicating that a global or sub-block configuration has been applied) before modifying or retrieving an item. For unitary items applicable to the entire PPP instance, two APIs per item are provided: HAL_PPP_SetItem and HAL_PPP_GetItem.

The HAL_PPP_SetItem API performs the following actions:

Check the API parameters using dedicated assertions that can be enabled in debug mode, reducing the footprint in the final “release” application.

Ensure that the global state is HAL_PPP_STATE_IDLE (using dedicated assertions), meaning that a global configuration has already been applied.

When several sub-instances are available, check that the sub-instances are not in the “ACTIVE” state (using dedicated assertions, ensuring no sub-instance(s) are running).

When several process states are available, check that the processes are in the “IDLE” state (using dedicated assertions, ensuring no process is running).

Update the required peripheral configuration/control registers according to the user configuration item (using the appropriate LL configuration API).

Depending on the HAL PPP handle and implementation, update the handle internal variables used by the process according to the user configuration.

Depending on the peripheral, the configuration may require waiting for a confirmation flag (delayed configuration). In this case, a wait loop is used to confirm the configuration through the dedicated peripheral flag.

An intrinsic timeout define ( HAL_PPP_FLAG_TIMEOUT ) is used, implemented in stm32tnxx_hal_ppp.c with respect to the peripheral/product specification (not a public define). When the dedicated flag is confirmed, HAL_PPP_SetItem returns HAL_OK .

If an error occurs during the item configuration (a confirmation flag does not rise), the API returns HAL_ERROR .

When the item configuration takes effect immediately (no need to wait for a confirmation flag), the API returns HAL_OK immediately after setting the register item.

The HAL_PPP_GetItem API performs the following actions:

Check the API parameters using dedicated assertions that can be enabled in debug mode, reducing the footprint in the final “release” application.

Ensure that the global state is HAL_PPP_STATE_IDLE or HAL_PPP_STATE_ACTIVE, meaning that a valid global configuration has been applied.

Read the required peripheral configuration/control register using the corresponding LL API and return the item value.

Examples:

hal_status_t HAL_TIM_SetCounterMode(const hal_tim_handle_t *htim,

hal_tim_counter_mode_t counter_mode);

hal_tim_counter_mode_t HAL_TIM_GetCounterMode(const hal_tim_handle_t *htim);

hal_status_t HAL_UART_SetBaudRate(const hal_uart_handle_t *huart, uint32_t baudrate);

uint32_t HAL_UART_GetBaudRate(const hal_uart_handle_t *huart);

For a unitary item that is applicable to a specific sub-block of the PPP instance, and when the sub-block has several sub-instances, the unitary configuration APIs reflect the sub-instance in their naming and parameters. Two APIs per item are provided to handle sub-block unitary configuration: HAL_PPP_{SUBBLOCK}_Set{Subinstance}Item and HAL_PPP_{SUBBLOCK}_Get{Subinstance}Item . These APIs respectively perform the same actions as the HAL_PPP_SetItem / HAL_PPP_GetItem , with the difference that the target register field to be updated or read is specific to the given sub-block and/or sub-instance.

Example:

hal_status_t HAL_TIM_IC_SetChannelSource(const hal_tim_handle_t *htim,

hal_tim_channel_t channel,

hal_tim_channel_src_t channel_src);

hal_tim_channel_src_t HAL_TIM_IC_GetChannelSource(const hal_tim_handle_t *htim,

hal_tim_channel_t channel);

Linking HAL DMA driver to HAL PPP driver ¶

For each HAL driver that supports a DMA-based process, dedicated DMA linking APIs are provided: one DMA link API per process with an explicit, self-descriptive name.

Example:

#if defined (USE_HAL_UART_DMA) && (USE_HAL_UART_DMA == 1)

/**

* @brief Set DMA channel for Transmission.

* @param huart Pointer to a hal_uart_handle_t structure holding the UART instance.

* @param hdma_tx Pointer to a hal_dma_handle_t structure holding the DMA instance.

* @retval HAL_OK Channel successfully linked.

* @retval HAL_INVALID_PARAM hdma_tx is NULL.

*/

hal_status_t HAL_UART_SetTxDMA(hal_uart_handle_t *huart, hal_dma_handle_t *hdma_tx)

{

ASSERT_DBG_PARAM(huart != NULL);

ASSERT_DBG_PARAM(hdma_tx != NULL);

ASSERT_DBG_STATE(huart->global_state, HAL_UART_STATE_CONFIGURED);

ASSERT_DBG_STATE(huart->tx_state, (uint32_t)(HAL_UART_TX_STATE_IDLE | HAL_UART_TX_STATE_RESET));

#if defined(USE_HAL_CHECK_PARAM) && (USE_HAL_CHECK_PARAM == 1)

if (hdma_tx == NULL)

{

return HAL_INVALID_PARAM;

}

#endif /* USE_HAL_CHECK_PARAM */

huart->hdma_tx = hdma_tx;

hdma_tx->p_parent = huart;

return HAL_OK;

}

/**

* @brief Set DMA channel for Reception.

* @param huart Pointer to a hal_uart_handle_t structure holding the UART instance.

* @param hdma_rx Pointer to a hal_dma_handle_t structure holding the DMA instance.

* @retval HAL_OK Channel successfully linked.

* @retval HAL_INVALID_PARAM hdma_rx is NULL.

*/

hal_status_t HAL_UART_SetRxDMA(hal_uart_handle_t *huart, hal_dma_handle_t *hdma_rx)

{

ASSERT_DBG_PARAM(huart != NULL);

ASSERT_DBG_PARAM(hdma_rx != NULL);

ASSERT_DBG_STATE(huart->global_state, HAL_UART_STATE_CONFIGURED);

ASSERT_DBG_STATE(huart->rx_state, (uint32_t)(HAL_UART_RX_STATE_IDLE | HAL_UART_RX_STATE_RESET));

#if defined(USE_HAL_CHECK_PARAM) && (USE_HAL_CHECK_PARAM == 1)

if (hdma_rx == NULL)

{

return HAL_INVALID_PARAM;

}

#endif /* USE_HAL_CHECK_PARAM */

huart->hdma_rx = hdma_rx;

hdma_rx->p_parent = huart;

return HAL_OK;

}

#endif /* USE_HAL_UART_DMA */

Key points: - Per process (TX, RX, etc.) a distinct API is required (no multiplexed generic linker). - State assertions ensure the peripheral is configured and the specific process is idle or reset. - Runtime NULL pointer checks are guarded by USE_HAL_CHECK_PARAM to reduce release footprint. - The DMA handle back-pointer (p_parent) is set to allow DMA callbacks to reach the owning HAL peripheral.

Setting and Getting user data ¶

When a HAL PPP driver is built around a handle, it allows the user to associate user data with the given handle.

An application should be able to store and retrieve a user data pointer into and from the HAL PPP handle. Since the data type and format can vary from one application to another, the user data pointer within the handle is a pointer to

void.

The HAL is not permitted to modify the user data; therefore, the pointer within the handle is a

const

void

*

pointer.

The HAL PPP driver provides two APIs to set and get the user data pointer as follows:

#if defined (USE_HAL_PPP_USER_DATA) && (USE_HAL_PPP_USER_DATA == 1)

/**

* @brief Store User Data pointer into the handle.

* @param hppp Pointer to a hal_ppp_handle_t.

* @param p_user_data Pointer to the user data.

*/

void HAL_PPP_SetUserData(hal_ppp_handle_t *hppp, const void *p_user_data)

{

/* Check the PPP handle allocation */

ASSERT_DBG_PARAM((hppp != NULL));

hppp->p_user_data = p_user_data;

}

/**

* @brief Retrieve User Data pointer from the handle.

* @param hppp Pointer to a hal_ppp_handle_t.

* @retval Pointer to the user data.

*/

const void * HAL_PPP_GetUserData(const hal_ppp_handle_t *hppp)

{

/* Check the PPP handle allocation */

ASSERT_DBG_PARAM((hppp != NULL));

return (hppp->p_user_data);

}

#endif /* USE_HAL_PPP_USER_DATA == 1 */

Note

The HAL does not perform any kind of treatment or checks on this user data pointer, except initializing it to NULL in HAL_PPP_Init . Thereafter, this pointer fully belongs to the user. The HAL only stores it in the handle and then restores it to the user as is through the appropriate HAL_PPP_SetUserData and HAL_PPP_GetUserData APIs.

HAL process and I/O operation APIs ¶

The HAL processing APIs offer a set of functions designed to manage data processing for various peripherals in a microcontroller. These APIs support three primary methods of data processing: Polling, Interrupt ( IT ), and Direct Memory Access ( DMA ), referred to as _XXX in the following code snippet. Additionally, for specific peripherals such as FDCAN, a fourth method may be available, which relies on user monitoring to determine the end of the process. Note that only the polling process APIs ( HAL_PPP_Process ) take a timeout parameter in milliseconds (timeout_ms).

In all these methods, the following initial steps are required:

Check all parameters validity (handle included) using asserts.

hal_status_t HAL_PPP_Process_XXX(hal_ppp_handle_t *hppp, const void *p_data, uint32_t size_byte, ...)

{

ASSERT_DBG_PARAM(hppp != NULL);

ASSERT_DBG_PARAM(p_data != NULL);

ASSERT_DBG_PARAM(size_byte != 0);

(...)

}

Check the state(s) validity to proceed with the requested process using asserts.

hal_status_t HAL_PPP_Process_XXX(hal_ppp_handle_t *hppp, const void *p_data, uint32_t size_byte, ...)

{

(...)

/* Check the global state IDLE or CONFIGURED depending on the implementation */

ASSERT_DBG_STATE(hppp->global_state, HAL_PPP_STATE_IDLE);

/* Check the Process state when available/applicable */

ASSERT_DBG_STATE(hppp->process_i_state, HAL_PPP_PROCESSi_STATE_IDLE);

(...)

}

Check the vital parameters under the compilation switch USE_HAL_CHECK_PARAM

hal_status_t HAL_PPP_Process_XX(hal_ppp_handle_t *hppp, const void *p_data, uint32_t size_byte)

{

(...)

#if defined(USE_HAL_CHECK_PARAM) && (USE_HAL_CHECK_PARAM == 1)

/* Check input parameters */

if ((p_data == NULL) || (size_byte == 0U))

{

return HAL_INVALID_PARAM;

}

#endif /* USE_HAL_CHECK_PARAM */

(...)

}

Convert the instance stored in the handle to the physical instance as per the CMSIS device (note that a dedicated private PPP_GET_INSTANCE macro is provided to allow this action for the various functions provided by the given HAL PPP driver).

#define PPP_GET_INSTANCE(handle) ((PPP_TypeDef *)((uint32_t)(handle)->instance))

(...)

hal_status_t HAL_PPP_Process_XXX(hal_ppp_handle_t *hppp, const void *p_data,

uint32_t size_byte, uint32_t timeout_ms)

{

(...)

PPP_TypeDef *p_pppx;

p_pppx = PPP_GET_INSTANCE(hppp);

(...)

}

Move the state from the initial required state (usually IDLE state) to the corresponding state of the given process using the macro HAL_CHECK_UPDATE_STATE

/* in case of a global state machine only (no dedicated state machine per process) */

HAL_CHECK_UPDATE_STATE(hppp, hppp->global_state, HAL_PPP_STATE_IDLE, HAL_PPP_STATE_ACTIVE);

/* in case of a dedicated state machine per process */

HAL_CHECK_UPDATE_STATE(hppp, process_i_state, HAL_PPP_PROCESSi_STATE_IDLE, HAL_PPP_PROCESSi_STATE_ACTIVE);

Reset the error code variable within the handle under the compilation switch USE_HAL_PPP_GET_LAST_ERRORS:

/* case of one single variable to hold the last error codes within the handle */

#if defined (USE_HAL_PPP_GET_LAST_ERRORS) && (USE_HAL_PPP_GET_LAST_ERRORS == 1)

hppp->last_error_codes = 0;

#endif /* USE_HAL_PPP_GET_LAST_ERRORS */

/* case of a variable to hold the last error codes per process within the handle */

#if defined (USE_HAL_PPP_GET_LAST_ERRORS) && (USE_HAL_PPP_GET_LAST_ERRORS == 1)

hppp->last_process_i_error_codes = 0;

#endif /* USE_HAL_PPP_GET_LAST_ERRORS */

Polling/blocking model ¶

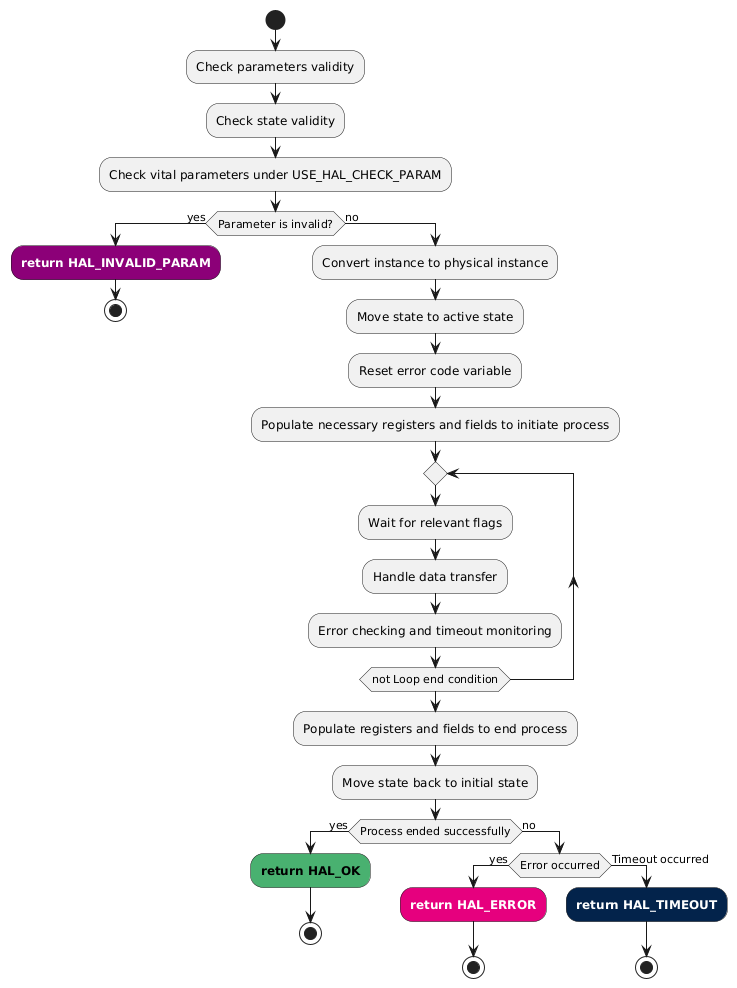

The Polling APIs in the Hardware Abstraction Layer (HAL) are designed to manage peripheral operations using a blocking approach. These APIs typically follow a standard naming convention, such as HAL_PPP_Process , where PPP represents the specific peripheral (e.g., UART, I2C, SPI) and Process denotes the I/O operation (e.g., Transmit, Receive, Encrypt, Decrypt). The HAL_PPP_Process function continuously checks the status of the peripheral until the desired condition is met, such as the completion of a data transmission or reception. During this period, the CPU remains engaged in polling the peripheral’s status registers, ensuring that the operation is fully completed before proceeding. This approach is straightforward and easy to implement, making it suitable for simple applications where the CPU can afford to wait. However, it can lead to inefficient use of CPU resources, as the CPU is unable to perform other tasks while polling. Despite this drawback, the Polling APIs provide a reliable method for managing peripheral operations in scenarios where precise timing and multitasking are not critical. After applying the required initial steps ( 1 to 6 ), the polling processes sequence shall be implemented as follows:

Once the various checks are completed and the state is transitioned to the required one according to the given process, the necessary registers and fields should be populated to initiate the process.

Enter a loop to continuously manage the data feeding into the peripheral or retrieving data from the peripheral. This involves:

Waiting for the relevant flags to indicate that the data is ready to be written to or read from the peripheral.

Ensuring that the data transfer is handled efficiently and accurately, maintaining the integrity of the process.

Within this loop, perform the following additional tasks:

Error Checking: Accumulate errors within the appropriate handle field under the compilation switch USE_HAL_PPP_GET_LAST_ERRORS.

Timeout Monitoring: Monitor the elapsed time and compare it to the user-given timeout.

The loop terminates under the following conditions:

Completion: All data are processed within the given user timeout.

Blocking Error: A blocking error occurs, making it impossible to continue the process.

Timeout: The operation exceeds the given user timeout.

When the processing loop ends, perform the following actions:

Populate the necessary registers and fields to end the process properly.

Move the state back to the initial required state (usually the HAL_PPP_STATE_IDLE state) by directly setting the appropriate handle state field.

Return the appropriate status code:

HAL_OK if the process ended successfully.

HAL_ERROR if an error occurred.

HAL_TIMEOUT if the process could not be finalized within the user-given timeout.

Interrupt asynchronous model ¶

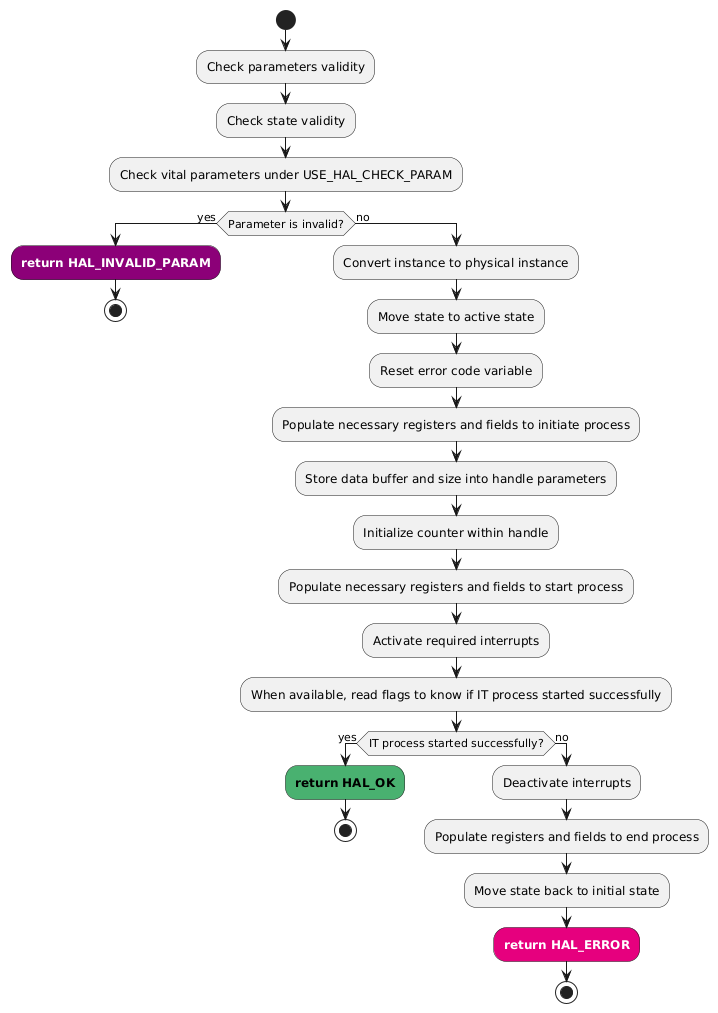

The Interrupt ( _IT ) model in the HAL leverages hardware interrupts to manage peripheral operations efficiently. In this model, the HAL_PPP_Process_IT API initiates a peripheral operation, arms the required interrupts at the peripheral level to ensure data processing, and then returns control to the caller, allowing the CPU to proceed with other tasks. When the peripheral completes the operation or reaches a specified condition (such as an input ready interrupt or output data available interrupt), it generates an interrupt signal to notify the CPU. The CPU then temporarily halts its current tasks to execute an interrupt service routine ( ISR ) that calls the appropriate HAL_PPP_IRQHandler to handle the peripheral’s data processing. This approach allows for more efficient use of CPU resources, as the CPU can perform other operations while waiting for the interrupt, making it ideal for applications that require multitasking and timely responses. The _IT model is particularly beneficial in scenarios where precise timing and efficient CPU utilization are critical.

In the Interrupt ( _IT ) model, it is forbidden to use blocking statements that depend on the HAL Time Base (such as HAL_Delay or functions relying on the system tick). Any required blocking operations, such as filling or emptying FIFOs, are managed in a tickless manner, for example by using CPU cycle counting. This restriction ensures that interrupt-driven processes can be safely executed within an ISR or callback , without introducing dependencies or conflicts with the system tick.

After applying the required initial steps (1 to 6), The HAL_PPP_Process_IT sequence is implemented as follows:

Once the various checks are completed and the state is moved to the required one for the process, the HAL_PPP_Process_IT function should perform the following actions:

Store the data buffer pointer and size in the corresponding handle fields.

Initialize a counter in the handle (for example, xfer_count) to track the remaining amount of data to process; this counter is decremented by HAL_PPP_IRQHandler on each interrupt.

hal_status_t HAL_PPP_Process_IT(hal_ppp_handle_t *hppp, const void *p_data, uint32_t size_byte)

{

(...)

hppp->p_buff = p_data;

hppp->xfer_size = size_byte;

hppp->xfer_count = size_byte;

(...)

}

Populate the necessary registers and fields to initiate the process. Depending on the peripheral, this may include writing an initial amount of data from the given data buffer into the peripheral register to start the process.

Activate the required interrupts to handle data processing, control, and error catching (IT model).

Return from the function, allowing the CPU to continue with other tasks. The actual data processing will be handled in the IT context.

If the IT* process did not start successfully due to an internal peripheral error signaled by a specific flag, perform the following actions:

Populate the necessary registers and fields to end the process properly (including interrupts deactivation and various flags clearing).

Move the state back to the initial required state (usually the HAL_PPP_STATE_IDLE state) by directly setting the appropriate handle state field.

Return the appropriate status code (HAL_ERROR).

DMA asynchronous model ¶

The Direct Memory Access (DMA) model in the HAL leverages general purpose DMA controllers to manage peripheral operations efficiently, offloading data transfer tasks from the CPU. Before calling HAL_PPP_Process_DMA , the user should first link the given HAL DMA handle to the HAL PPP handle using the appropriate API (e.g., HAL_UART_SetTxDMA ).

The HAL_PPP_Process_DMA API initiates the peripheral operation then starts a DMA to handle data transfers between memory and the peripheral, or vice versa. The API then returns control to the caller, allowing the CPU to proceed with other tasks.

The HAL DMA callbacks (half transfer, transfer complete, transfer error) are set by the HAL_PPP_Process_DMA to internal PPP functions that handle these events. These internal functions ensure the process is properly completed and report the completion to the user through the various HAL PPP callbacks. This means that the HAL DMA callbacks are not user callbacks in this context but are intercepted by the HAL PPP itself. Essentially, the DMA acts as a service peripheral for the PPP peripheral.

The DMA controller autonomously handles the data transfer, generating interrupts to notify the CPU upon completion or when specific conditions are met, such as transfer complete or transfer error. The CPU temporarily halts its current tasks to execute the corresponding DMA channel interrupt service routine (ISR) that calls the appropriate HAL_DMA_IRQHandler to manage the completion of the data processing. The HAL_DMA_IRQHandler will trigger the various DMA callbacks that are set to internal HAL PPP callbacks, as explained above.

This approach allows for highly efficient use of CPU resources, as the CPU can perform other operations while the DMA controller manages data transfers in the background. The DMA model is particularly advantageous in scenarios where large amounts of data need to be transferred quickly and efficiently, and where minimizing CPU involvement is critical.

Same as IT model, in the DMA model, it is forbidden to use blocking statements that depend on the HAL Time Base ( IT dependency). Instead, any necessary blocking statements, such as filling or dumping FIFOs, are managed in a tickless mode, utilizing CPU cycle counting. This restriction ensures that DMA processes can be safely called within an ISR or callbacks without causing conflicts or dependencies on the system tick.

The HAL_PPP_Process_DMA applies the same required initial steps ( 1 to 6 ) with a particular emphasis on step 3. Specifically, the DMA handle corresponding to the given process is considered a vital parameter that should not be null and thus is checked under the USE_HAL_CHECK_PARAM compilation flag. Concretely, this means that a DMA handle should be properly linked to the PPP handle prior to running the given process.

hal_status_t HAL_PPP_Process_DMA_Opt(hal_ppp_handle_t *hppp, const void *p_data, uint32_t size_byte)

{

(...)

#if defined(USE_HAL_CHECK_PARAM) && (USE_HAL_CHECK_PARAM == 1)

/* Check input parameters */

if ((p_data == NULL) || (size_byte == 0U) || (hppp->hdma_i == NULL))

{

return HAL_INVALID_PARAM;

}

#endif /* USE_HAL_CHECK_PARAM */

(...)

}

After applying the required initial steps ( 1 to 6 ), the HAL_PPP_Process_DMA sequence is implemented as follows:

Once the various checks are completed and the state is transitioned to the required one according to the given process, the HAL_PPP_Process_DMA function:

Store the data buffer and size into the corresponding handle pointer parameters.

hal_status_t HAL_PPP_Process_DMA(hal_ppp_handle_t *hppp, const void *p_data, uint32_t size_byte)

{

(...)

hppp->p_buff = p_data;

hppp->xfer_size = size_byte;

hppp->xfer_count = size_byte;

(...)

}

Set the DMA callbacks to the dedicated internal PPP functions that will intercept these DMA events

hal_status_t HAL_PPP_Process_DMA(hal_ppp_handle_t *hppp, const void *p_data, uint32_t size_byte)

{

(...)

/* Set the PPP DMA transfer complete callback */

hppp->hdma_i->p_xfer_cplt_cb = PPP_DMAProcessCplt;

/* Set the PPP DMA Half transfer complete callback */

hppp->hdma_i->p_xfer_halfcplt_cb = PPP_DMAProcessHalfCplt;

/* Set the DMA error callback */

hppp->hdma_i->p_xfer_error_cb = PPP_DMAError;

(...)

}

9. Start the DMA transfer by calling the HAL_DMA_StartPeriphXfer_IT_Opt function. Set the source and destination parameters to the user input buffer and the peripheral data register, respectively, based on the transfer direction (read or write). The last parameter of this function allows control over optional DMA interrupts (e.g., half transfer). Typically, this parameter is set to HAL_DMA_OPT_IT_DEFAULT , which enables the default set of DMA interrupts. If the PPP process does not require optional DMA interrupts, such as the half transfer interrupt, you can set this parameter to HAL_DMA_OPT_IT_NONE .

In case the DMA transfer did not start successfully, perform the following actions:

Set the last error code field in the handle to indicate a DMA error.

Move the state back to the initial required state (usually the HAL_PPP_STATE_IDLE state) by directly setting the appropriate handle state field.

Return HAL_ERROR.

hal_status_t HAL_PPP_Process_DMA(hal_ppp_handle_t *hppp, const void *p_data, uint32_t size_byte)

{

(...)

if (HAL_DMA_StartPeriphXfer_IT_Opt(hppp->hdma_i, (uint32_t)&p_pppx->DR,

(uint32_t)hppp->p_buff, size_byte, HAL_DMA_OPT_IT_DEFAULT) != HAL_OK)

{

#if defined (USE_HAL_PPP_GET_LAST_ERRORS) && (USE_HAL_PPP_GET_LAST_ERRORS == 1)

hppp->last_process_i_error_codes |= HAL_PPP_PROCESSi_ERROR_DMA;

#endif /* USE_HAL_PPP_GET_LAST_ERRORS */

hppp->process_i_state = HAL_PPP_PROCESSi_STATE_IDLE;

return HAL_ERROR;

}

(...)

}

10. Populate the necessary registers and fields to initiate the process. Depending on the peripheral, this may include activating specific control PPP interrupts. These interrupts will be intercepted by the HAL_PPP_IRQHandler itself. Note that even in a DMA model, certain interrupts may be necessary to control the process at the PPP level.

11. Enable the DMA request from the peripheral to the DMA by writing to the appropriate register field using the dedicated LL API. Note that, depending on the peripheral, after enabling the DMA request at the PPP level, you may need to explicitly enable the PPP by writing to the appropriate register field using the corresponding LL API.

If the DMA process starts successfully, return HAL_OK and leave the data processing to be handled as follows:

DMA Handling: The DMA itself will manage the data transfer and signal various steps, such as half transfer, transfer complete, or errors, to the HAL PPP driver through the appropriate callbacks.

PPP Interrupt Handling: The HAL_PPP_IRQHandler will manage control and error handling, if any.

13. Process Completion Signaled by the DMA: The process completion is indicated by the corresponding DMA callback (transfer complete or error callbacks) that are set by the HAL PPP itself. Upon process completion, the implementation of the PPP_DMAProcessCplt and PPP_DMAError callbacks take care of the following actions:

Populate the necessary PPP registers and fields to properly end the process, including deactivating interrupts (if any) and clearing various flags.

Disable the DMA requests from the PPP to the DMA.

Update the PPP state back to the initial required state (usually the IDLE state) by directly setting the appropriate HAL PPP handle state field.

Call the corresponding HAL PPP callback to inform the user about the end of the process, whether it ended successfully or with an error.

Process Completion Signaled by a PPP Error Interrupt: In case the peripheral provides error management, the HAL_PPP_IRQHandler acts as follows when a blocking error interrupt occurs:

Store the error code to the corresponding HAL PPP handle field.

Disable the DMA requests from the PPP to the DMA.

Set the DMA abort callback to a dedicated internal PPP function that will intercept the DMA abort event and end the process properly, including:

Populate the necessary PPP registers and fields to end the process properly, deactivate interrupts (if any), and clear various flags.

Update the state back to the initial required state (usually the IDLE state) by directly setting the appropriate handle state field.

Call the corresponding HAL PPP error callback to inform the user.

Aborting an asynchronous process ¶

The HAL_PPP_Abort and HAL_PPP_Abort_IT functions are provided to abort any ongoing asynchronous process, including interrupt ( IT ) and DMA processes. For a given PPP instance, HAL_PPP_Abort is a synchronous, blocking function that stops the current data transfer, disables the peripheral, clears any error flags, and puts the handle state back to the IDLE state.

Conversely, HAL_PPP_Abort_IT is an asynchronous, non-blocking function that initiates the abort of an ongoing asynchronous process and returns immediately, allowing the application to continue executing other tasks. The actual stopping of the data transfer and resetting of the handle state is handled by the interrupt service routine ( ISR ) associated with the ongoing asynchronous process, which calls a dedicated callback to signal the completion of the abort process. This function is suitable for scenarios where the abort process can be handled in the background without blocking the main application flow.

Asynchronous model, filtering optional interrupts ¶

The conventional HAL PPP asynchronous processes (IT and DMA) usually enable all the interrupts related to the given process. Some of these interrupts are mandatory (e.g., Transfer Complete), while others are informative and not mandatory for the HAL process (e.g., Half Transfer). In addition to these conventional asynchronous processes, the HAL provides users with ways to filter the optional interrupts. For analog peripherals (ADC, DAC, and TIM), a silent asynchronous mode is also provided: a non-blocking mode with DMA in circular mode and without interrupt signaling.

To address these needs, the HAL provides additional IT and DMA process APIs with an _Opt postfix: HAL_PPP_Process_IT_Opt and HAL_PPP_Process_DMA_Opt , with the following rules:

API Prototypes:

These APIs have the same prototype as the original process APIs but with an additional uint32_t interrupts parameter that indicates the optional interrupts to be enabled.

This interrupts parameter can be a combination of several optional interrupts.

Dedicated defines are provided to be used for the interrupts parameter.

Defines for Optional Interrupts:

Clear All Optional Interrupts: One define to clear all the optional interrupts: HAL PPP OPT NONE (the numerical value zero).

DMA Silent Mode: One define to select the DMA silent mode: HAL PPP OPT DMA SILENT (i.e., the DMA asynchronous process does not issue any DMA interrupt).

Optional Interrupt Defines: Defines are provided for each process (IT and DMA) per interrupt:

HAL PPP OPT DMA {PROCESS#i} IT {interrupt_name}

HAL PPP OPT IT {PROCESS#i} IT {interrupt_name}

Behavior Based on interrupts Parameter:

When the interrupts parameter is set to HAL PPP OPT NONE, all optional interrupts are disabled for the given process.

When the interrupts parameter is set to HAL PPP OPTDMA SILENT, the DMA-based process operates in DMA silent mode (the DMA used by the given peripheral does not issue interrupts).

When the interrupts parameter is set to HAL PPP OPT IT {PROCESS#i} DEFAULT or HAL PPP OPT DMA {PROCESS#i} DEFAULT, the HAL PPP Process IT Opt or HAL PPP Process DMA Opt APIs behave the same as the conventional HAL PPP Process IT or HAL PPP Process DMA.

DMA Driver API:

The DMA driver provides a HAL_DMA_StartPeriphXfer_Opt API with an additional interrupts parameter. This parameter allows filtering optional interrupts or starting the DMA in silent mode (i.e., without any enabled interrupt). This API is used by the HAL PPP driver to implement the HAL_PPP_Process_DMA_Opt APIs.

Examples:

Optional defines:

/** UART_Optional_Interrupts UART Optional Interrupts */

/** UART_Transmit_IT_Optional_Interrupts UART Optional Interrupts for Transmit interrupt process */

/*! Do not activate optional interruptions on TX IT process */

#define HAL_UART_OPT_TX_IT_NONE 0U

/*! Activate FIFO Empty optional interruption */

#define HAL_UART_OPT_TX_IT_FIFO_EMPTY (1U << 30U)

/*! Activate Clear To Send optional interruption */

#define HAL_UART_OPT_TX_IT_CLEAR_TO_SEND (1U << 29U)

/*! Activate FIFO Empty and Clear To Send optional interruptions */

#define HAL_UART_OPT_TX_IT_DEFAULT (HAL_UART_OPT_TX_IT_FIFO_EMPTY | HAL_UART_OPT_TX_IT_CLEAR_TO_SEND)

#if defined (USE_HAL_UART_DMA) && (USE_HAL_UART_DMA == 1U)

/* UART_Transmit_DMA_Optional_Interrupts UART Optional Interrupts for Transmit DMA process */

/*! Do not activate optional interruptions on TX DMA process */

#define HAL_UART_OPT_DMA_TX_IT_NONE 0U

/*! Activate DMA Half Transfer optional interruption */

#define HAL_UART_OPT_DMA_TX_IT_HT (HAL_DMA_OPT_IT_HT)

/*! Activate DMA Half Transfer optional interruption */

#define HAL_UART_OPT_DMA_TX_IT_DEFAULT (HAL_UART_OPT_DMA_TX_IT_HT)

#if defined(USE_HAL_DMA_LINKEDLIST) && (USE_HAL_DMA_LINKEDLIST == 1)

/*! Activate Silent Mode on DMA */

#define HAL_UART_OPT_DMA_TX_IT_SILENT (HAL_DMA_OPT_IT_SILENT)

#endif /* USE_HAL_DMA_LINKEDLIST */

IT based process: To avoid duplicating code between the HAL_PPP_Process_IT and HAL_PPP_Process_IT_Opt APIs, it is recommended to provide a private function that implements the process, taking the optional interrupts parameter. In this case, the public functions perform the necessary parameter and state checks, and then call the private function to proceed with the process.

static hal_status_t UART_Start_Transmit_IT(hal_uart_handle_t *huart, const uint8_t *p_data, uint32_t size,

uint32_t interrupts);

hal_status_t HAL_UART_Transmit_IT(hal_uart_handle_t *huart, const void *p_data, uint32_t size_byte)

{

ASSERT_DBG_PARAM(huart != NULL);

(...)

ASSERT_DBG_STATE(huart->global_state, HAL_UART_STATE_CONFIGURED);

ASSERT_DBG_STATE(huart->tx_state, HAL_UART_TX_STATE_IDLE);

#if defined(USE_HAL_CHECK_PARAM) && (USE_HAL_CHECK_PARAM == 1)

/* Check input parameters */

if ((p_data == NULL) || (size_byte == 0U))

{

return HAL_INVALID_PARAM;

}

#endif /* USE_HAL_CHECK_PARAM */

HAL_CHECK_UPDATE_STATE(huart, tx_state, HAL_UART_TX_STATE_IDLE, HAL_UART_TX_STATE_ACTIVE);

return UART_Start_Transmit_IT(huart, (const uint8_t *)p_data, size_byte, HAL_UART_OPT_TX_IT_NONE);

}

hal_status_t HAL_UART_Transmit_IT_Opt(hal_uart_handle_t *huart, const void *p_data, uint32_t size_byte,

uint32_t interrupts)

{

ASSERT_DBG_PARAM(huart != NULL);

(...)

ASSERT_DBG_PARAM(IS_UART_OPT_TX_IT(interrupts));

ASSERT_DBG_STATE(huart->global_state, HAL_UART_STATE_CONFIGURED);

ASSERT_DBG_STATE(huart->tx_state, HAL_UART_TX_STATE_IDLE);

#if defined(USE_HAL_CHECK_PARAM) && (USE_HAL_CHECK_PARAM == 1)

/* Check input parameters */

if ((p_data == NULL) || (size_byte == 0U))

{

return HAL_INVALID_PARAM;

}

#endif /* USE_HAL_CHECK_PARAM */

HAL_CHECK_UPDATE_STATE(huart, tx_state, HAL_UART_TX_STATE_IDLE, HAL_UART_TX_STATE_ACTIVE);

return UART_Start_Transmit_IT(huart, (const uint8_t *)p_data, size_byte, interrupts);

}

hal_status_t UART_Start_Transmit_IT(hal_uart_handle_t *huart, const uint8_t *p_data, uint32_t size,

uint32_t interrupts)

{

(...)

/* enable the optional interrupts when selected */

if ((interrupts & HAL_UART_OPT_TX_IT_FIFO_EMPTY) == HAL_UART_OPT_TX_IT_FIFO_EMPTY)

{

LL_USART_EnableIT_TXFE(p_uartx);

}

if ((interrupts & HAL_UART_OPT_TX_IT_CLEAR_TO_SEND) == HAL_UART_OPT_TX_IT_CLEAR_TO_SEND)

{

LL_USART_EnableIT_CTS(p_uartx);

}

(...)

return HAL_OK;

}

DMA based process:

To avoid duplicating code between the HAL_PPP_Process_DMA and HAL_PPP_Process_DMA_Opt APIs, a private function is recommended to implement the process, taking the optional interrupts parameter.

Private Function Implementation: Create a private function that handles the DMA process, accepting an optional interrupts parameter. This private function masks the given interrupts with those related to the PPP peripheral and activates the enabled ones.

It should then call the HAL_PPP_Process_DMA_Opt function with the last parameter being the interrupts masked with the DMA-specific optional interrupts.

Public Functions: The public functions HAL_PPP_Process_DMA and HAL_PPP_Process_DMA_Opt perform the necessary parameter and state checks. After the checks, they call the private function to proceed with the process.

By following this approach, code duplication is minimized, and the implementation becomes more maintainable and efficient.

static hal_status_t UART_Start_Transmit_DMA(hal_uart_handle_t *huart, const uint8_t *p_data, uint32_t size,

uint32_t interrupts);

hal_status_t HAL_UART_Transmit_DMA(hal_uart_handle_t *huart, const void *p_data, uint32_t size_byte)

{

ASSERT_DBG_PARAM(huart != NULL);

(...)

ASSERT_DBG_STATE(huart->global_state, HAL_UART_STATE_CONFIGURED);

ASSERT_DBG_STATE(huart->tx_state, HAL_UART_TX_STATE_IDLE);

#if defined(USE_HAL_CHECK_PARAM) && (USE_HAL_CHECK_PARAM == 1)

/* Check input parameters */

if ((p_data == NULL) || (size_byte == 0U))

{

return HAL_INVALID_PARAM;

}

#endif /* USE_HAL_CHECK_PARAM */

HAL_CHECK_UPDATE_STATE(huart, tx_state, HAL_UART_TX_STATE_IDLE, HAL_UART_TX_STATE_ACTIVE);

return UART_Start_Transmit_DMA(huart, (const uint8_t *)p_data, size_byte, HAL_UART_OPT_DMA_TX_IT_HT);

}

hal_status_t HAL_UART_Transmit_DMA_Opt(hal_uart_handle_t *huart, const void *p_data, uint32_t size_byte,

uint32_t interrupts)

{

ASSERT_DBG_PARAM(huart != NULL);

(...)

ASSERT_DBG_PARAM(IS_UART_OPT_TX_DMA(interrupts));

#if defined(USE_HAL_DMA_LINKEDLIST) && (USE_HAL_DMA_LINKEDLIST == 1)

ASSERT_DBG_PARAM(IS_UART_DMA_TX_VALID_SILENT_MODE(huart->hdma_tx, interrupts));

#endif /* USE_HAL_DMA_LINKEDLIST */

ASSERT_DBG_STATE(huart->global_state, HAL_UART_STATE_CONFIGURED);

ASSERT_DBG_STATE(huart->tx_state, HAL_UART_TX_STATE_IDLE);

#if defined(USE_HAL_CHECK_PARAM) && (USE_HAL_CHECK_PARAM == 1)

/* Check input parameters */

if ((p_data == NULL) || (size_byte == 0U))

{

return HAL_INVALID_PARAM;

}

#endif /* USE_HAL_CHECK_PARAM */

HAL_CHECK_UPDATE_STATE(huart, tx_state, HAL_UART_TX_STATE_IDLE, HAL_UART_TX_STATE_ACTIVE);

return UART_Start_Transmit_DMA(huart, (const uint8_t *)p_data, size_byte, interrupts);

}

hal_status_t UART_Start_Transmit_DMA(hal_uart_handle_t *huart, const uint8_t *p_data, uint32_t size,

uint32_t interrupts)

{

uint32_t interrupts_dma;

(...)

#if defined(USE_HAL_DMA_LINKEDLIST) && (USE_HAL_DMA_LINKEDLIST == 1)

if (interrupts == HAL_UART_OPT_DMA_TX_IT_SILENT)

{

interrupts_dma = HAL_UART_OPT_DMA_TX_IT_SILENT;

}

else

#endif /* USE_HAL_DMA_LINKEDLIST */

{

interrupts_dma = (interrupts & HAL_UART_OPT_DMA_TX_IT_HT);

}

(...)

if (HAL_DMA_StartPeriphXfer_IT_Opt(huart->hdma_tx, (uint32_t)huart->p_tx_buff, (uint32_t)&p_uartx->TDR,

size, interrupts_dma) != HAL_OK)

{

huart->tx_state = HAL_UART_TX_STATE_IDLE;

#if defined (USE_HAL_UART_GET_LAST_ERRORS) && (USE_HAL_UART_GET_LAST_ERRORS == 1)

huart->last_transmission_error_codes |= HAL_UART_TRANSMIT_ERROR_DMA;

#endif /* USE_HAL_UART_GET_LAST_ERRORS */

return HAL_ERROR;

}

}

(...)

if (((interrupts & HAL_UART_OPT_TX_IT_CLEAR_TO_SEND) == HAL_UART_OPT_TX_IT_CLEAR_TO_SEND)

#if defined(USE_HAL_DMA_LINKEDLIST) && (USE_HAL_DMA_LINKEDLIST == 1)

&& (interrupts_dma != HAL_UART_OPT_DMA_TX_IT_SILENT)

#endif /* USE_HAL_DMA_LINKEDLIST */

)

{

LL_USART_EnableIT_CTS(p_uartx);

}

return HAL_OK;

}

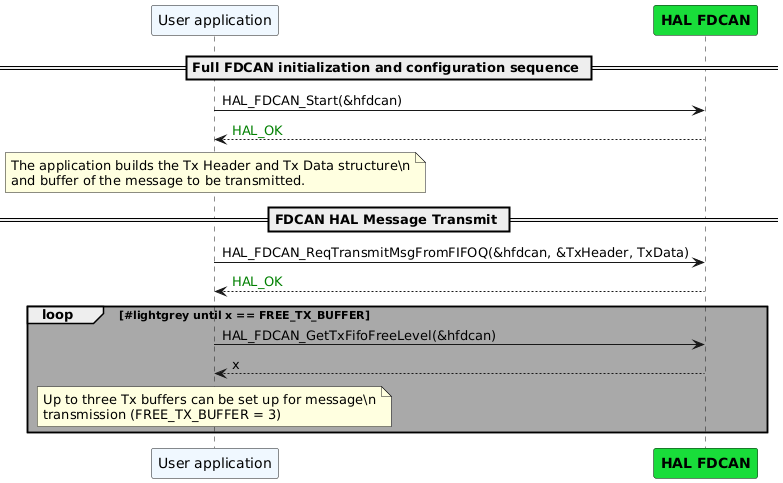

Monitoring model ¶

For some peripherals, data processing can be fully handled by the peripheral itself without the need for the CPU to continuously manage data feeding or retrieval in a unitary way. Instead, the CPU needs to provide the full data frame to the peripheral in one shot or read the full received data frame in one shot.

In such cases, the peripheral usually provides internal FIFOs and buffers that can contain the full message or frame. It also provides flags and interrupts indicating that the data frames are processed and available, as well as indicators on the FIFO (Tx/Rx) levels in frames. This is the case with FDCAN peripherals, which provide internal FIFOs and buffers, autonomously handle CAN frame sending and receiving, and signal the user about the end of the process and the availability of data/frames upon receiving.

In this scenario, a single monitoring process should be proposed instead of conventional polling and interrupt-driven processes. The HAL driver should provide the following:

An API to start the peripheral.

Transmission or Writing Direction:

An API to feed the entire data or frame to the internal peripheral FIFO or buffer in one shot.

An API to enable the transmission/processing interrupts.

Receiving or Reading Direction:

An API to read the entire received frame or data in one shot.

An API to check if a new received frame is available, or to get the receiving/processed output FIFO level (e.g., number of received frames).

An API to enable the receiving/processing interrupts.

The user can implement the monitoring process flexibly at the application level using either a blocking or non-blocking method.

Blocking Method:

Transmission or Writing Direction: Continuously check the internal Tx FIFO level to know if the peripheral is ready to process/send a new frame. Use the appropriate API to feed the peripheral with the new frame to send.

Receiving or Reading Direction: Continuously check the internal Rx FIFO level to know if the peripheral received one or several frames and retrieve them using the appropriate API.

Non-Blocking Method:

Transmission or Writing Direction: Enable the transmission/processing frame complete interrupt(s). Within the corresponding callback, take appropriate actions to check the Tx FIFO level and feed the peripheral with the new frame(s) to send.

Receiving or Reading Direction: Enable the receiving/processing complete interrupt(s). Within the corresponding callback, take appropriate actions to check the Rx FIFO level and read the received frame(s) from the peripheral.

The user can implement the monitoring process flexibly at the application level using either a blocking or non-blocking method.

Blocking Method:

Transmission or Writing Direction: Continuously check the internal Tx FIFO level to know if the peripheral is ready to process/send a new frame. Use the appropriate API to feed the peripheral with the new frame to send.

Receiving or Reading Direction: Continuously check the internal Rx FIFO level to know if the peripheral received one or several frames and retrieve them using the appropriate API.

Non-Blocking Method:

Transmission or Writing Direction: Enable the transmission/processing frame complete interrupt(s). Within the corresponding callback, take appropriate actions to check the Tx FIFO level and feed the peripheral with the new frame(s) to send.

Receiving or Reading Direction: Enable the receiving/processing complete interrupt(s). Within the corresponding callback, take appropriate actions to check the Rx FIFO level and read the received frame(s) from the peripheral.

By following this approach, the user can implement a flexible and efficient monitoring process at the application level.

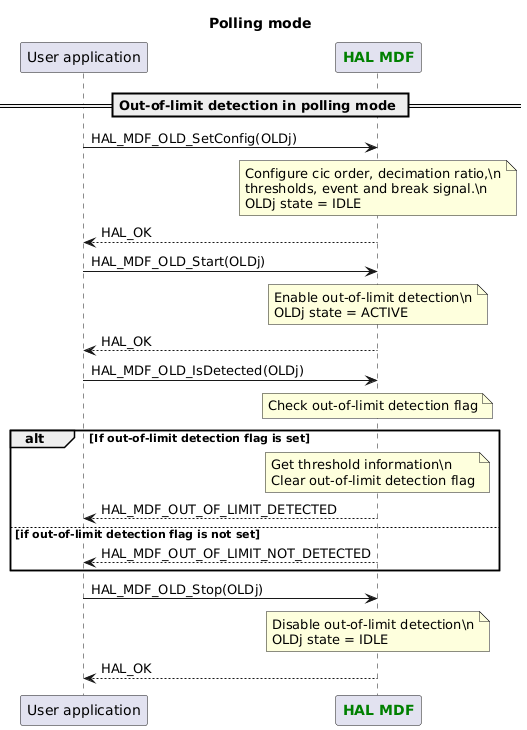

Examples of user processing:

The monitoring model can also be useful for tracking additional events signaled by the peripheral, in addition to the main data processes. In this case, the HAL driver should provide APIs to start the monitoring process with or without interrupts, an API to check if a specific event has been detected (useful for users who need to implement a monitoring task or loop), and a dedicated callback function to signal the event (useful for users who prefer asynchronous interception of the event). This approach allows users to implement a flexible and efficient monitoring process at the application level, capable of handling both main data processes and additional peripheral events, using either a blocking method by continuously checking for events or a non-blocking method by relying on interrupts and callbacks for asynchronous event handling.

Examples of user events monitoring:

HAL IRQ Handler and callback ¶

HAL IRQ Handler ¶

The

HAL_PPP_IRQHandler()

ISR function is called from the corresponding

PPPi_IRQHandler

(generated in

mx_pppi.c).

It manages the peripheral interrupt events and maintains the process state machine accordingly. When an interrupt event is asserted and is associated

with a functional state (error, completion, notification), a callback is called to inform the user asynchronously about these events (refer to

Registering user callbacks to the HAL drivers).

When an interrupt is enabled, there are two models to handle it depending on the peripheral interrupt hardware management:

Model 1 (check for Interrupt sources register and event flags):

Check for the interrupt source bits.

Check for the event flag.

Clear the event status.

Process the event.

void HAL_PPP_IRQHandler(hal_ppp_handle_t *hppp)

{

PPP_TypeDef *p_pppx = PPP_GET_INSTANCE(hppp);

uint32_t error_code = HAL_PPP_ERROR_NONE;

/* read the Interrupt enable register */

uint32_t ier_it = LL_PPP_READ_REG(p_pppx, ier_reg); /* IER: Interrupt Enable register */

/* read the Interrupt status register */

uint32_t isrflags = LL_PPP_READ_REG(p_pppx, isr_reg); /* ISR: Interrupt Status register */

/* PPP ERR1 error interrupt occurred -------------------------------------*/

if (((isrflags & PPP_ISR_ERR1) != 0U) && ((ier_it & PPP_IER_ERR1IE) != 0U))

{

LL_PPP_ClearFlag_ERR1(p_pppx); /* clear the ERR1 interrupt flag */

error_code = HAL_PPP_ERROR_ERR1;

}

(...)

/* PPP ERRn error interrupt occurred -------------------------------------*/

if (((isrflags & PPP_ISR_ERRn) != 0U) && ((ier_it & PPP_IER_ERRnIE) != 0U))

{

LL_PPP_ClearFlag_ERRn(p_pppx); /* clear the ERRn interrupt flag */

error_code |= HAL_PPP_ERROR_ERRn;

}

#if defined (USE_HAL_PPP_GET_LAST_ERRORS) && (USE_HAL_PPP_GET_LAST_ERRORS == 1)

hppp->last_error_codes |= error_code;

#endif

if (error_code != HAL_PPP_ERROR_NONE)

{

/* call the Error callback */

#if defined (USE_HAL_PPP_REGISTER_CALLBACKS) && (USE_HAL_PPP_REGISTER_CALLBACKS == 1)

hppp->p_error_cb(hppp);

#else

HAL_PPP_ErrorCallback(hppp);

#endif

}

(...)

/* Process the event */

if (((isrflags & PPP_ISR_EVENT1) != 0U) && ((ier_it & PPP_IER_EVENT1) != 0U))

{

LL_PPP_ClearFlag_EVENT1(p_pppx); /* clear the EVENT1 interrupt flag */

#if defined (USE_HAL_PPP_REGISTER_CALLBACKS) && (USE_HAL_PPP_REGISTER_CALLBACKS == 1)

hppp->p_eventi_cb(hppp);

#else

HAL_PPP_EventiCallback(hppp);

#endif /* USE_HAL_PPP_REGISTER_CALLBACKS == 1 */

}

/* Process completion */

if (((isrflags & PPP_ISR_COMPLETION_MSK) != 0U) && ((ier_it & PPP_IER_COMPLETION_MSK) != 0U))

{

LL_PPP_ClearFlag_COMPLETION(p_pppx); /* clear the completion flags */

/* Disable the process interrupts */

LL_PPP_DisableIT(p_pppx, completion_msk); /* or can use LL_PPP_READ_REG/ LL_PPP_WRITE_REG to disable the given process interrupts in the IER:

Interrupt Enable register */

/* update the global state to IDLE */

hppp->global_state = HAL_PPP_STATE_IDLE; /* case of a single process at a time */

/* or update the process state to IDLE */

hppp->processi_state = HAL_PPP_STATE_PROCESSi_IDLE;

#if defined (USE_HAL_PPP_REGISTER_CALLBACKS) && (USE_HAL_PPP_REGISTER_CALLBACKS == 1)

hppp->p_processi_cplt_cb(hppp);

#else

HAL_PPP_ProcessiCpltCallback(hppp);

#endif /* USE_HAL_PPP_REGISTER_CALLBACKS == 1 */

}

}

Model 2 (check Interrupt Status Register):

Check for the interrupt status.

Clear the interrupt status.

Process the event.

void HAL_PPP_IRQHandler(hal_ppp_handle_t *hppp)

{

PPP_TypeDef *p_pppx = PPP_GET_INSTANCE(hppp);

uint32_t error_code = HAL_PPP_ERROR_NONE;

uint32_t isrflags = LL_ReadReg(p_pppx, <status_reg>);

/* Knowing that the error code values are mapped/defined as the Error register Fields */

error_code = LL_ReadReg(p_pppx, <err_reg>);

LL_PPP_ClearFlags(p_pppx); /* clear the interrupt flags */

if (PPP_CHECK_FLAG(error_code, PPP_FLAG_<ERR1>))

{

error_code = HAL_PPP_ERROR_ERR1;

}

(...)

if (PPP_CHECK_FLAG(error_code, PPP_FLAG_<ERRn>))

{

error_code |= HAL_PPP_ERROR_ERRn;

}

#if defined (USE_HAL_PPP_GET_LAST_ERRORS) && (USE_HAL_PPP_GET_LAST_ERRORS == 1)

hppp->last_error_codes |= error_code;

#endif

if (error_code != HAL_PPP_ERROR_NONE)

{

#if defined (USE_HAL_PPP_REGISTER_CALLBACKS) && (USE_HAL_PPP_REGISTER_CALLBACKS == 1U)

hppp->p_error_cb(hppp);

#else

HAL_PPP_ErrorCallback(hppp);

#endif /* USE_HAL_PPP_REGISTER_CALLBACKS == 1U */

}

/* Process the event */

if (PPP_CHECK_FLAG(isrflags, PPP_FLAG_EVENT1) != RESET)

{

#if defined (USE_HAL_PPP_REGISTER_CALLBACKS) && (USE_HAL_PPP_REGISTER_CALLBACKS == 1U)

hppp->p_event1_cb(hppp);

#else

HAL_PPP_Event1Callback(hppp);

#endif /* USE_HAL_PPP_REGISTER_CALLBACKS == 1U */

}

/* Process completion */

if ((isrflags & PPP_ISR_COMPLETION_MSK) != 0U)

{

/* Disable the process interrupts */

LL_PPP_DisableIT(p_pppx);

/* update the global state to IDLE */

hppp->global_state = HAL_PPP_STATE_IDLE; /* case of a single process at a time */

/* or update the process state to IDLE */

hppp->processi_state = HAL_PPP_STATE_PROCESSi_IDLE;

#if defined (USE_HAL_PPP_REGISTER_CALLBACKS) && (USE_HAL_PPP_REGISTER_CALLBACKS == 1U)

hppp->p_processi_cplt_cb(hppp);

#else

HAL_PPP_ProcessiCpltCallback(hppp);

#endif /* USE_HAL_PPP_REGISTER_CALLBACKS == 1U */

}

}

Note

Interrupt and flag registers are read once and saved locally to prevent race conditions and optimize register access within IRQ handlers.

HAL callbacks ¶

The asynchronous process models (Interrupt model and DMA model) allow synchronization with the user application through dedicated callbacks. HAL callbacks are invoked by the HAL PPP driver when the corresponding event occurs. A separate callback is provided for each event, including process completion, half-completion, abort completion, and error handling. For some peripherals, callbacks should also cover asynchronous events related to hardware control and monitoring. For example, the HAL LTDC provides a callback to signal that the LTDC has reached a specific line during display, and the HAL FDCAN should inform when frames are received.